微处理器的性能指标最主要为两项:

- 字长:CPU能同时处理的数据位数,也成为数据宽度

- 主频:CPU的时钟频率,主频越高运算速度越快

16位微处理器

内部组成

8086为16位微处理器,有16根内部总线和20根地址总线,因此可寻址空间大导2^20字节,即1MB

从功能上8086分为两部分,总线接口部件(BIU)和执行部件(EU)

总线接口部件

负责与存储器,IO端口传输数据。即总线接口部件从内存取指令送到指令队列。CPU执行指令时,总线接口要配合执行部件从指定的内存单元或外设接口中取数据,将数据传送给执行部件,或把执行部件的操作结果传送给指定的内存单元或外设中

组成

- 四个段地址寄存器(CS代码段,DS数据段,ES附加段,SS堆栈段)

- 16位指令寄存器IP

- 20位地址加法器(物理地址=CS段寄存器内容左移4位+IP指令指针寄存器内容)

- 6字节指令队列缓冲器

执行部件

负责指令的执行

组成

- 四个通用寄存器(AX,BX,CX,DX)

- 四个专用寄存器(BP,SP,SI,DI)

- 标志寄存器FR

- 算术逻辑部件ALU

总线周期

8086中一个最基本的总线周期由4个时钟周期组成

- 时钟周期为CPU的基本时间计量单位,由主频决定,若主频f=5MHz,则时钟周期T=1/f=200ns

- 总线周期为CPU从存储器或IO端口存取一个单位所需要的时间

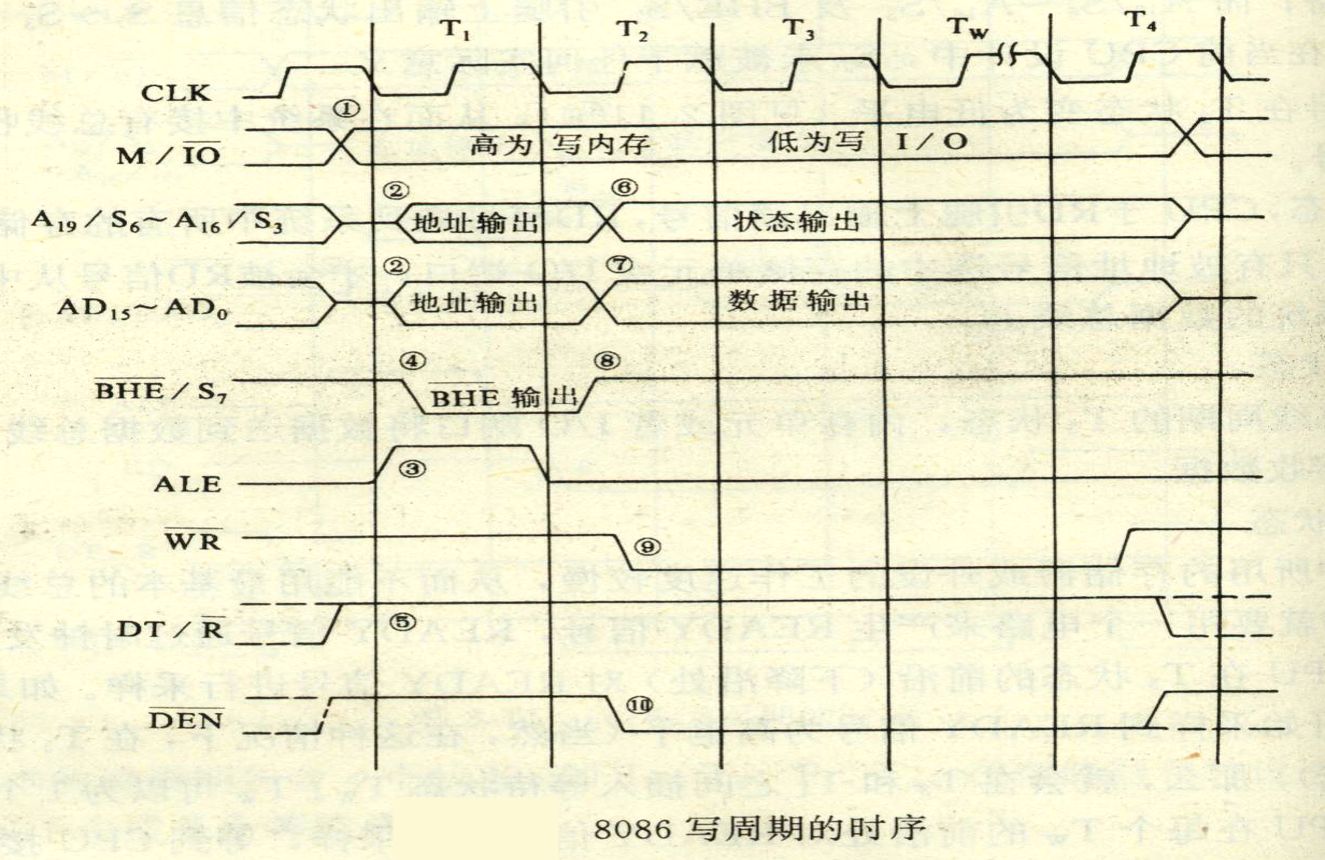

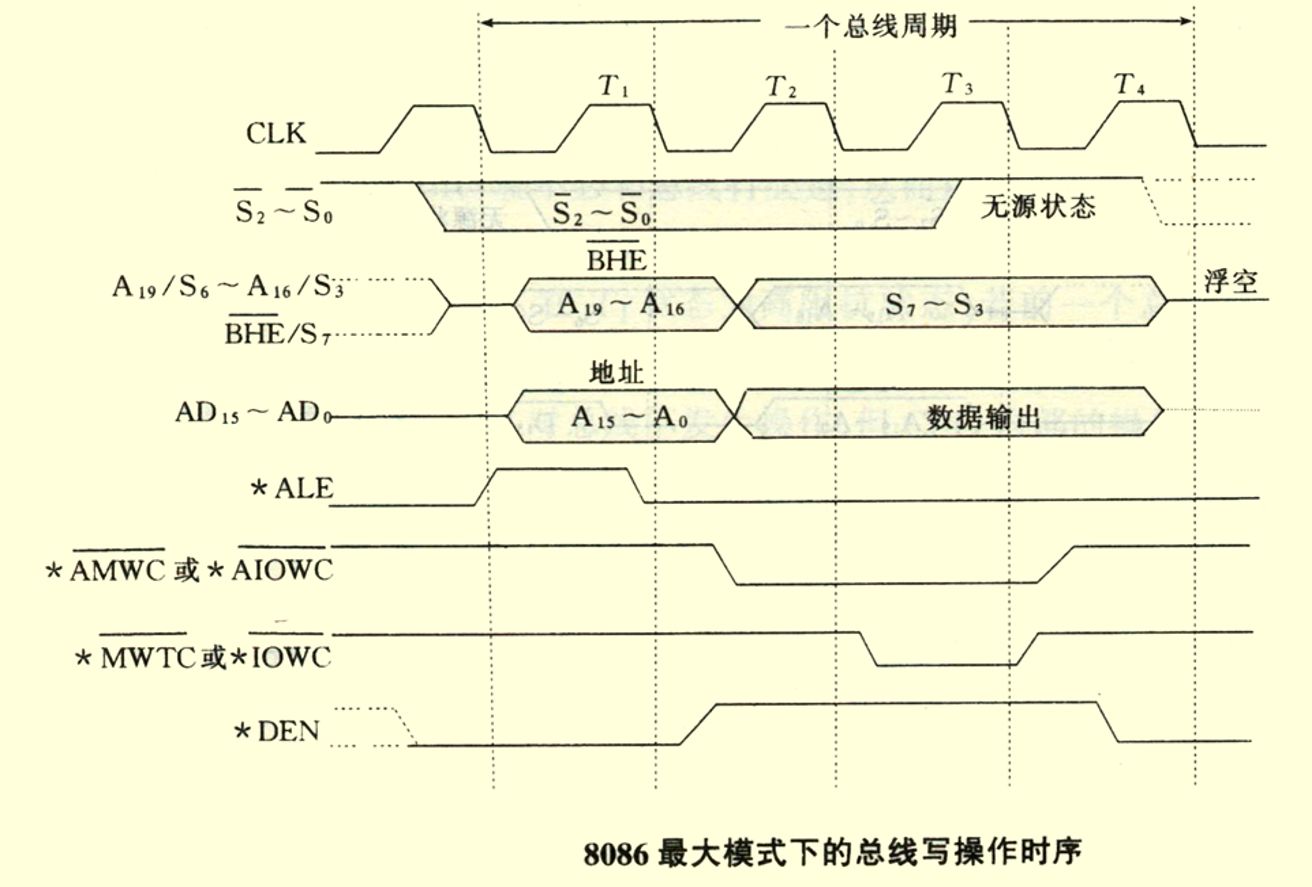

- T1状态:CPU向总线发送地址信息指出要寻址的存储单元或外设端口地址

- T2状态:CPU总总线上撤销地址,总线低16位高阻态为接收数据做准备,高4位输出总线的周期状态信息

- T3状态:总线低16位出现cpu写入或从存储器/外设读入的数据

- Tw状态(可选):数据若未准备好,CPU在T3状态之后插入一个或多个Tw等待状态,直到在READY信号线上接受到已准备好的信号

- T4状态:总线周期结束

- Ti状态(可选):一个周期结束后不立即执行下一个总线周期,则系统总线处于空闲状态Ti

引脚信号与工作模式

最小模式即在系统中只有8086一个处理器,所有总线控制信号都直接由8086产生,最大模式中包含有两个或多个微处理器,8086主处理器和其他协处理器(数值运算8087,输入输出8089),8086工作在哪个模式由硬件连线决定

- CLK时钟信号

- NMI非屏蔽中断请求信号

- INTR可屏蔽中断请求信号

- RD读信号,输出

- MN/MX最大最下工作模式控制信号,高最小,低最大

- READY准备好信号

- TEST测试信号,与WAIT结合使用,每五个时钟周期检测

- RESET复位信号

- BHE/S7高八位数据总线允许/状态复用引脚,T1时输出BHE表示AD15-8有效,T234w时输出状态信号S7

- INTA中断响应信号

- ALE地址锁存允许信号

- DEN数据允许信号

- DT/R数据收发输出方向控制信号,高为输出,低为输入

- M/IO存储器,IO控制信号,高为访问存储器,低为访问IO设备

- WR写信号

- HOLD总线保持请求信号

- HLDA总线保持响应信号

下面八根信号线与工作模式相关,最大工作模式下,总线控制信号既可以由8086产生也可以协处理器产生

- S2/S1/S0总线周期状态信号

- RQ/GT0总线请求输入,总线请求允许信号输出

- RQ/GT1总线请求输入,总线请求允许信号输出,优先级低于上面

- LOCK总线封锁信号

- QS1/QS0指令队列状态信号

操作与时序

系统的复位和启动

复位操作由RESET信号发出,RESET信号进入高电平,CPU停止现在的操作,将CS设置为初值0FFFFH,IP为0000H,其他内部寄存器设置为0,因此复位操作之后再重新启动时,从内存的FFFF0H处开始执行指令,因此一般在FFFF0H处放置一个无条件转移指令,转移到系统程序的入口处;此外,在复位时各种标志寄存器都被清零因此所有INTR进入的可屏蔽中断都不被允许,因此需要开放中断指令STI来设置中断允许标志

最小工作模式读周期

T1:地址A0-19上线,ALE下降沿锁存地址,DT/R低电平持续到T4,低为输入,高为输出

T2:A19-16变为S3-S7,DEN有效打开数据线,RD有效执行读操作,AD0-15为高阻态为输入数据做准备

T3:D15-0到数据线,CPU得到数据,次状态若READY为低电平则插入Tw

T4:数据消失,控制信号复位,为下一个总线周期做准备

最小工作模式写周期

最大工作模式读周期

最大工作模式与最小类似,区别在于在最大模式下,总线控制信号均由8288发出,且不是单纯的读写信号,而是根据指令发出的具体的读写存储器或I/O口的信号。

最大工作模式写周期

中断

- 中断正常运行程序时,由于内部或外部某个紧急事件发生,使CPU暂停真噶子运行的程序,在执行完当前指令后,转去执行请求中断的外设或事件的中断处理程序,处理完后返回继续执行正常的程序

- 中断源引起中断的事件

- 断点主程序被打断的位置

- 中断服务程序对中断源的响应或处理程序

- 中断向量中断服务程序的入口地址包含基址与偏移地址两部分,占用四个字节

- 中断类型码8086最多可处理256种中断0-255,专用中断0-4,保留中断5-31,用户中断32-255

- 中断向量表从物理地址

00000H开始,一次存放中断向量,形成专门储存中断服务入口地址的存储区域。256个不同类型中断占1kb区域,00000H-003FFH - 中断向量地址指针中断向量在中断向量表中存放的首地址,=中断类型码*4

若中断类型码为42H的中断向量为5678H:1234H

则中断向量表的00108H-0010B中依次存放34H,12H,78H,56H

中断响应流程

8086的存储器编址

8086有20根地址线,具有1MB存储器地址空间,内存单元按照00000-FFFFFH来编址,由于指令指针,堆栈指针都是16位,要计算一个存储单元的物理地址,线将段寄存器左移4位,加上16位的偏移量(有效地址)得到物理地址

8086的IO编址

8086允许有65535个8位IO端口,两个相邻的8位端口可以组成一个16位端口

- 独立编址方式访问IO端口

- cpu使用低16位地址线寻址IO端口

32位微处理器

指令流水线

Pentium指令流水线由总线接口部件、指令预取部件、指令译码部件和执行部件构成。

超标量:配置多个执行部件和指令译码电路,能同时执行多条指令。

Pentium由三个执行单元组织而成,一个执行浮点指令,另两个执行整型指令(U流水线和V流水线),这意味着Pentium同时可以执行三条指令

整数流水线

五个阶段

- PF 预取 处理器从代码cache中预取指令

- D1 译码阶段1 对指令译码确定操作吗与寻址信息

- D2 译码阶段2 产生访问存储器的地址

- EX 执行 处理器访问数据cache,或利用ALU等计算单元计算结果

- WB 写回 使用运行结果更新寄存器与标志寄存器

流水线:在CPU中把一条指令分解成多个可单独处理的操作,使每个操作在一个专门的硬件站(stage)上执行,这样一条指令需要顺序地经过流水线中多个站的处理才能完成,但是前后相连的几条指令可以依次流入流水线中,在多个站间重叠执行,因此可以实现指令的并行处理。

浮点流水线

八个阶段

- PF 预取

- D1 译码阶段1

- D2 译码阶段2

- EX 取操作数

- X1 浮点执行步骤1

- X2 浮点执行步骤2

- WT 写浮点数

- ER 出错报告

寄存器功能

基本寄存器组

- 通用寄存器

- AX 累加器

- BX 基址寄存器

- CX 计数寄存器

- DX 数据寄存器

- 指令指针寄存器

- SP 堆栈指针寄存器,指示堆栈在内存中的位置

- BP 基数指针寄存器,存放数据在内存中的基地址

- SI 源操作数变址寄存器,存放源数据的地址

- DI 目的操作数变址寄存器,存放目的数据的地址

- IP 存放指令代码在内存中的相对地址

- 标志寄存器

- FR 存放CPU当前状态

- CF 进位标志

- PF 奇偶标志

- AF 半进位标志

- ZF 零标志

- SF 符号位标志

- TF 单步标志

- IF 中断标志

- DF 方向标志,为1时,从高地址向低地址处理字符串

- OF 溢出标志

- 段寄存器

系统寄存器组

- 地址寄存器

- 控制寄存器

- 调试寄存器

- 测试寄存器

浮点寄存器组

- 数据寄存器

- 标记字寄存器

- 状态寄存器

- 控制字寄存器

- 指令指针寄存器

- 数据指针寄存器